dvt84893 - The simulation timescale is incorrect in some circumstances when running in -batch mode. This legacy switch forces incremental mode (pre-6.0 behavior) which is sub-optimal, and it is no longer maintained. Customer scripts using this switch will have to be changed.

In 10.8 or a subsequent release, the -novopt switch will not be accepted by the tool and cause tool to exit with error message. The -novopt switch will be accepted in 10.7 with a deprecation suppressible error message. (source, results) The -novopt command line switch will be deprecated in the next major release 10.7 following normal deprecation process: The transcript output in -batch mode now matches the output when using -c or -i modes in this regard. dvt94468 - (results) When using vsim -batch mode, the transcript (stdout) output could contain NUL and CR characters that are otherwise filtered out when using other vsim modes. dvt110375 - (results) In some cases simulation result differ between optimized and unoptimized cells with optimize cells selecting the wrong path delay when negative timing checks are present. src/iter1b.sv(11): Illegal use of solve/before constraint in conditional/implication constraint context. When the condition expression of IfElse constraint is NOT constant, a new runtime error (vsim-16056) will be thrown, i.e.Įrror: (vsim-16056). A compile error (vlog-2919) will be thrown if solve/before constraint is under an IfElse constraint. vlog/vopt -pedanticerrors or -svext=-ifslvbefr will revert back to the legacy behavior. By default, this extension is on and no compile-time check is triggered. dvt110034 - (source, results) Added a SV extension vlog/vopt -svext +-]ifslvbefr to allow solve/before constraint within an IfElse constraint with constant condition. Any differences will be flagged by the compiler with an error.

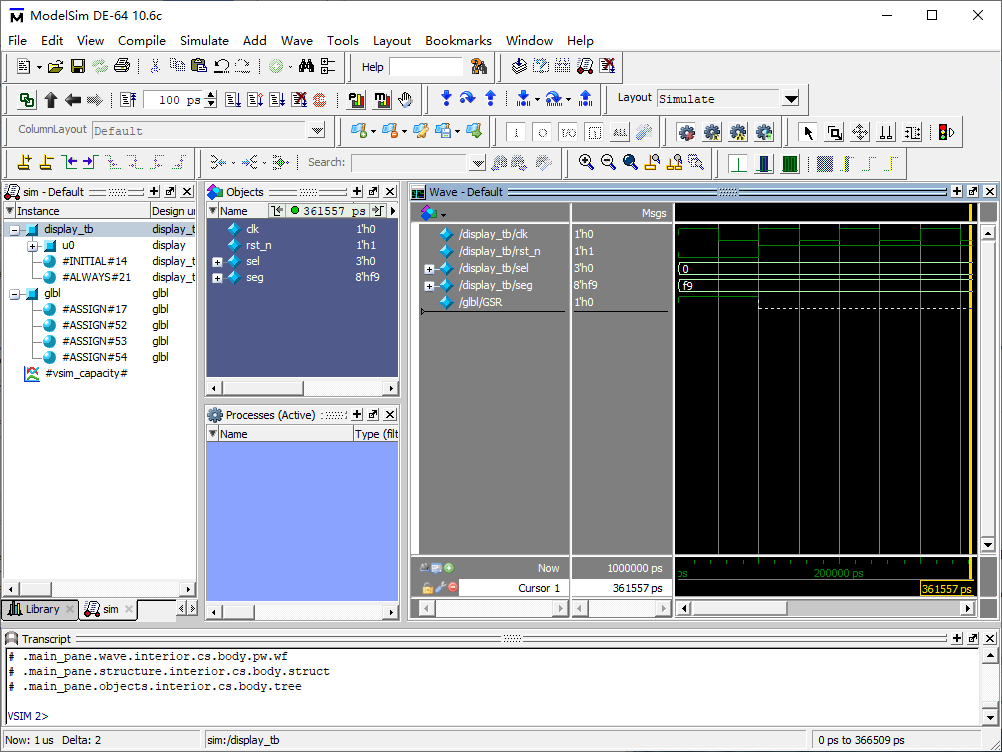

MODELSIM 10.6B CODE

This may cause SV HDL code to be compiled differently than with previous versions. (source) An issue with incorrect precedence in the & and "matches" operations in SV has been fixed. Improved Verilog/VHDL performance and optimizations Mentor, a Siemens business, has unveiled ModelSim 10.6e, is unified debug and simulation environment gives today's FPGA designers advanced capabilities in a productive work environment. Mentor Graphics ModelSim SE-64 10.6e | 814.2 mb

0 kommentar(er)

0 kommentar(er)